引 言

随着科学技术的发展,传统的雷达信号处理系统由于专用性强,兼容性差,影响了系统的通用性和其扩展能力,不能满足现代雷达实时高速的信号处理需求。设计通用并行信号处理系统己经成为高速实时信号处理发展的必然趋势,而基于CPCI总线的多DSP信号处理模板设计是该领域的研究热点之一。该设计针对传统雷达信号处理系统通用性和扩展能力差提出一种ADSP—TS201基于PCI9656桥芯片实现与CPCI总线通信的高速、通用性强的信号处理系统,并介绍一种DSP与PCI9656的接口电路设计。

1.器件介绍

1.1 ADSP—TS201

ADSP—TS201是ADI公司TigerSHARC系列中集成了定点和浮点计算功能的高速DSP。ADSP—TS201内部4条相互独立的128位宽度的内部数据总线,每条连接6个2 Mb内部存储区块中的一个,提供各自数据、指令集I/O访问和28 GB/s的内部存储器宽带;处理器内核最高可工作在600 MHz,单周期能执行4条指令,每秒能进行3.4亿次乘累加和2.8亿次浮点操作,是面向通信和视频领域的高端DSP。ADSP—TS201有14通道的DMA控制器;4个链路口可用于与其他DSP进行无缝联接,实现高速度高数据吞吐率。链路口可以4位并行方式传输,也可以编码为1位传输方式。通常以4位并行方式传输,当处理器核工作在500 MHz时,链路口也可工作在500 MHz,每个链路口的双向数据吞吐率可达1 000 MB/s,4个链路口合起来数据吞吐率可达4 GB/s;集成SDRAM控制器最大支持256 M×32 b的内存容量,方便与外部SDRAM连接。ADSP—TS201适合对大数据量数据处理实时性要求高的应用领域。TigerSHARC系列的DSP接口丰富,外部设备接口包括SDRAM控制器、EPRoM接口、主机接口、多处理器接口;其引导程序的加载方法也非常灵活,可根据实际系统设计的需要灵活选用。

1.2 PCI9656

PCI9656是PLX公司推出的与PCI9054相兼容的、能提供混合高性能PCI总线的接口控制芯片,采用了业界领先的数据流水线架构技术,符合PCI V2.2规范。PCI9656的工作状态包括以下两个方面:工作方式和局部总线操作模式。PCI9656的工作方式包括直接主模式、直接从模式和DMA模式,它的局部总线操作模式有M模式、C模式和J模式。它具有64位数据线66 MHz时钟的PCI总线接口和32位数据总线66 MHz时钟的Loeal端接口;配有的DMA引擎可实现数据的高速传输;具有PCI优先判决器,支持7个外部主控制器;可以通过消息管理I/O,提供两种方式选择,一是通过邮箱寄存器和门铃寄存器;二是通过所提供的I2O接口。它有64 b/66 MHz PCI性能,符合PCIV2.2规范,采用数据。设计者可以将芯片32 b,66 MHz局部总线与各类高速设备,如DSP、存储器、自定义ASIC和FPGA连接,通过PCI9656数据流水架构使其局部端连接设备具有64 b/66 MHz的PCII/O性能。

2.系统工作原理

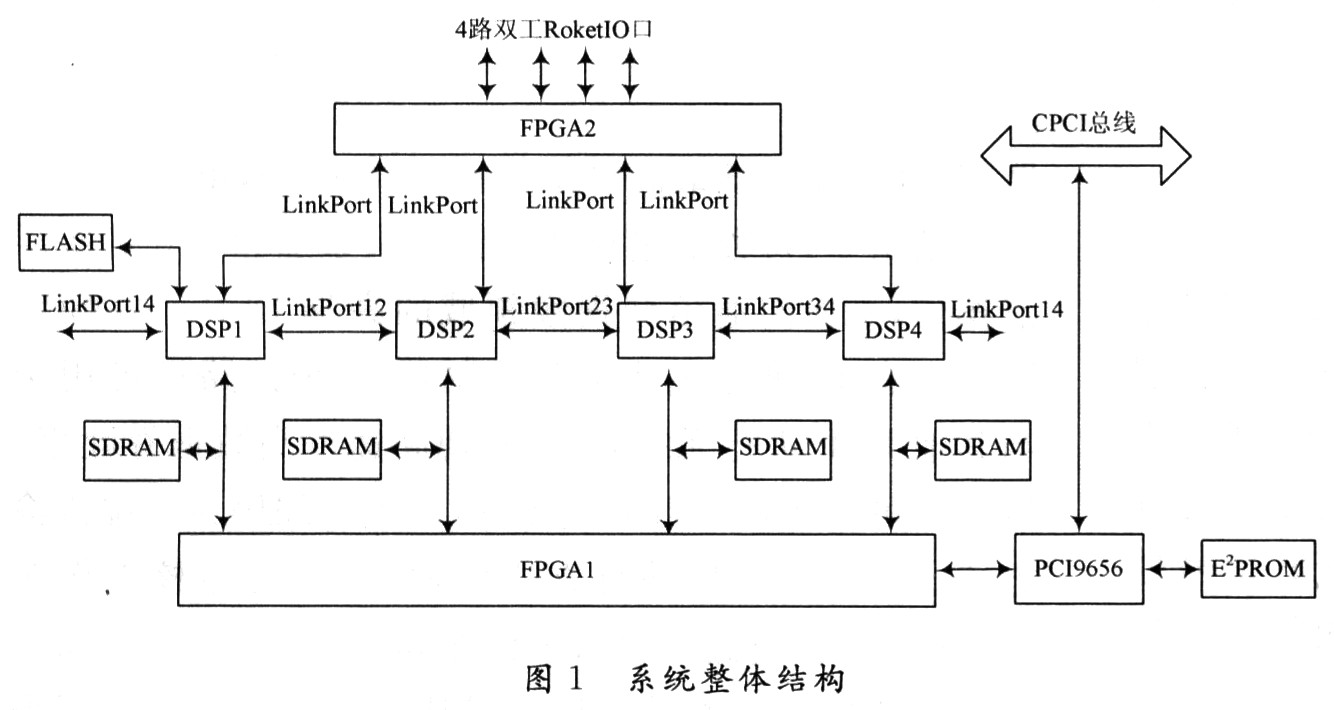

信号处理板上DSP的工作与主机相对独立,主机通过CPCI总线给信号处理板传送加载程序和一些控制信息,并监控信号处理板。采集数据通过4路全双工Rocket_IO口发送给信号处理板。系统的整体结构如图1所示。

2.1 DSP的电路设计

信号处理板中DSP对来自板外的采样数据进行数据整理、相参积累和脉冲压缩。4片DSP之间采用链路口方式实现点对点的通信。DSP采用主机与EPROM方式引导和加载程序,先通过FLASH将加载程序导入DSPl,然后用主机引导方式将传入DSP1内的加载程序依次传输给其他3片DSP。由于DSP有专用的SDRAM寻址空间和外围接口,DSP与SDRAM之间能实现无缝连接。该设计中每片DSP外挂1片256 Mb的SDRAM,保证了DSP足够的存储空间。

2.2 PCI9656与DSP连接设计

由于PCI9656与DSP接口不兼容,所以用逻辑转换器件FPGAl实现它们之间的连接。FPGAl中设计有一个能与ADSP—TS201S直接通信的主机接口模块,将ADSP-TS201S主机接口与FPGAl内的主机接口直接相连。PCI9656通过FPGAl内主机接口间接访问ADSP—TS201S。FPGAl中设计16 K×32 b的双口RAM,用于缓存PCI9656与DSP之间读写数据。FPGAl一端与4片DSP相连,另一端与PCI9656局部端相连。当出现多个DSP同时请求与PCI9656通信时,FPGAl内DSP开关选择模块对其进行仲裁。PCI9656根据主机的要求可以访问任意一片DSP。PCI9656对信号处理板上4片SDRAM的访问有2种方式。第一,通过DSP来间接的访问SDRAM,DSP先将SDRAM中数据读到其内部存储区,然后PCI9656通过访问DSP访问SDRAM;第二,在FPGAl内设计SDRAM控制器,通过FPGAl内控制器直接访问SDRAM。

2.3 PCI9656与CPCI总线连接设计

设计中信号处理板是6U规格,可与J1至J5五个连接头相连。J1是32位PCI总线,J2用于64位PCI总线或用户自定义I/O口;J3,J4和J5是用户自定义I/O口。为了保证信号处理板的通用性和可扩展性,J1与J2连接头作为64位数据宽度的CPCI总线。PCI9656一端与FPGAl相连另一端分别与儿和J2连接头相连。需要注意的是PCI9656与CPCI连接的引脚必须插入10 Ω的匹配电阻,以降低对背板的干扰。

2.4 Rocket_IO与DSP的连接设计

信号处理板通过全双工Rocket_IO口接收板外的采集数据,数据吞吐率可达1.25 Gb/s。FPGA2实现Rocket_IO与DSP的LinkPort之间的接口转换,其一端连接4路Rocket_IO口相连另一端连接每片DSP的1路LinkPort,即4路链路口。

DSP的每路链路口数据吞吐率可达,1 GB/s。FPGA2对.Rocket_IO口送入的数据整理后,利用链路口传输给相应的DSP。任意一路LinkPort能与任意一路的Rocket_IO口通信,当多路LinkPort争用一路Rocket_IO口或多路Rocket_IO口争用一路LinkPort时,FPGA2内的总线开关模块实现它们之间的仲裁。设计中信号处理板可以选用任意用户自定义IO口作为Rocket_IO通道。

3. PCI9656与DSP的接口设计

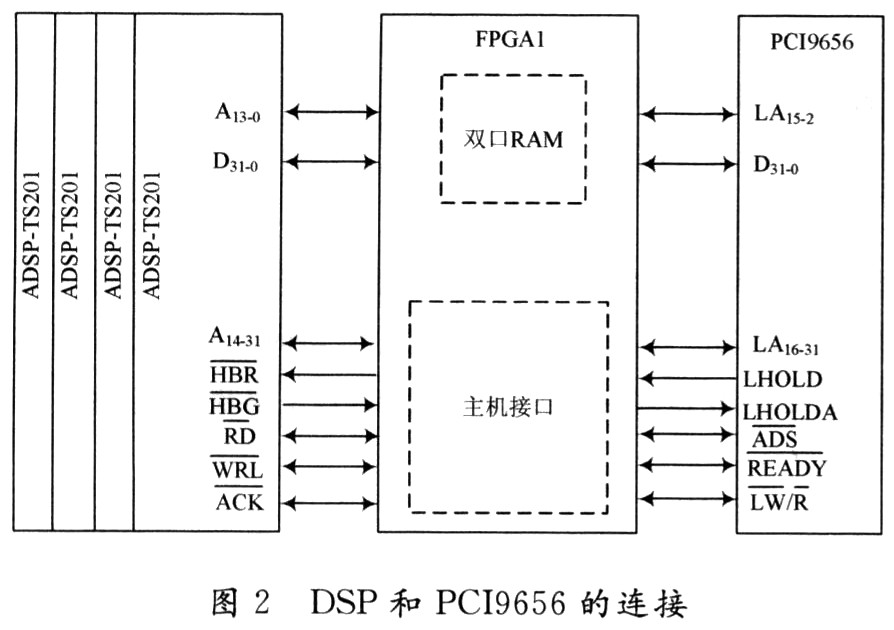

PCI9656的局部端采用C模式,32位数据和32位地址线。PCI9656配置为直接从模式,即只有主机可以通过PCI9656申请局部端总线控制权访问DSP。4片DSP与FPGAl连接方式相同,这里只给出1片DSP与PCI9656之间的接1:3逻辑转换。DSP和PCI9656的连接如图2所示。

PCI9656对DSP的访问通过FPGAl间接实现,FPGAl内设计有实现逻辑转换的主机接口模块、用于数据缓存的双口RAM模块和DSP开关选择模块。

3.1 PCI9656读DSP

(1)PCI9656使LHOLD变高申请局部总线控制权;FPGA检测到后,立即使LHOLDA变高,告知PCI9656局部总线申请成功。PCI9656使ADS和一LW/R变低,然后发送主机地址;FPGAl依据高位地址译码生成DSP片选信号,根据LW/R将主机接口配置为读方式,同时使PCI9656的READY信号无效。

(2)FPGAl向相应的DSP发HBR和RD申请总线控制权并请求读数据;DSP检测到HBR后返回HBG和ACK。FPGAl检测ACK到信号后,接收数据并缓存至双口RAM。当数据传输完毕时DSP使RD和ACK无效,撤销HBG,FPGAl接着撤销HBR。

(3)FPGAl使READY有效,PCI9656检测到该信号后,开始读取双口RAM中的数据。数据传输完毕后FPGAl使READY无效并收回LHOLDA,PCI9656接着撤消LHOLD,此次读操作结束。

3.2 PCI9656写DSP

(1)PCI9656使LHOLD变高申请局部总线控制权;FPGA检测到后,立即回应使LHOLDA变高告知PCI9656局部总线申请成功。PCI9656使ADS变低、LW/R变高,然后发送主机地址;FPGAl根据高位地址译码生成DSP片选信号,根据LW/R将主机接口配置为写方式,同时使能PCI9656的READY。

(2)PCI9656检测到READY后,将数据写入双口RAM。数据传输完毕后PCI9656使READY无效,收回LHOLD;FPGAl接着撤消LHOLDA。

(3)FPGAl向相应的DSP发出HBR和WRL申请总线控制权并请求对DSP写数据操作,DSP检测到信号返回HBG和ACK。FPGAl检测到ACK信号后,开始将双口RAM中的数据发送给DSP。数据传输完毕后FPGA使WRL无效,撤销HBR;DSP接着撤销HBG和ACK。此次写操作完成。

4. 结 语

提出的基于CPCI总线的高速通用雷达信号处理板设计,继承了CPCI总线可靠、可扩展、通用性强的特点。PCI9656桥芯片和FPGAl逻辑转换芯片实现板外主机对DSP的访问。通过FPGA2将Rocket_IO口与DSP的LinkPort口互联实现数据的高速传输。 |