在雷达信号处理、数字图像处理等领域中,信号处理的实时性至关重要。由于FPGA芯片在大数据量的底层算法处理上的优势及DSP芯片在复杂算法处理上的优势,DSP+FPGA的实时信号处理系统的应用越来越广泛。ADI公司的TigerSHARC系列DSP芯片浮点处理性能优越,故基于这类DSP的DSP+FPGA处理系统正广泛应用于复杂的信号处理领域。同时在这类实时处理系统中,FPGA与DSP芯片之间数据的实时通信至关重要。

TS201 DSP的外部总线接口有两种协议:慢速协议和高速流水协议。流水线协议适合与快速同步设备连接,文中采用此协议,实现DSP与FPGA之间的通信。

1. DSP流水线协议

流水线协议用来提供流水线方式的数据传输。在该传输协议下,每个时钟周期可以传输一个数据。控制流水线协议进行数据传输的主要信号包含以下引脚:

RD――数据传输读信号;

WRH和WRL――数据传输写信号;

BRST――突发方式数据传输指示;

ADDR――地址总线;

DATA――数据总线。

流水线协议数据传输有两种方式:普通流水线协议和突发流水线协议。ADSP TS201的数据总线位宽可以通过SYSCON寄存器设置为32位或者64位,但是有时候需要传输的数据位宽可能是32位,64位或者128位,这样就有可能出现数据总线位宽和数据位宽不一致的情况,如果总线位宽小于数据位宽,DSP采用突发流水协议传输,否则采用普通流水线协议。

1.1 普通流水线协议

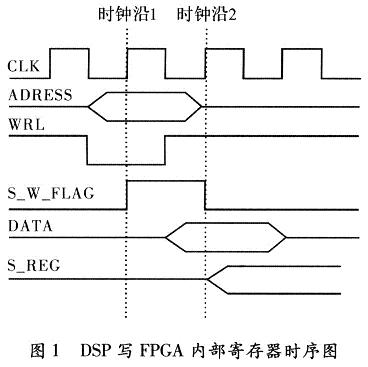

图1是DSP使用普通流水协议,写FPGA内部寄存器时序图,流水深度为1,在时钟沿1地址线、WRx(WRH和WRL)同时有效,一个时钟周期后,在时钟沿2数据线有效,地址线、WRx无效。

1.2 突发流水线协议

因为数据总线位宽小于数据位宽,那么它只能通过两次传输来完成。但是如果DSP没有任何指示信号,FPGA并不知道当前传输是高32位数据,还是低32位数据,这时候另外一个信号BURST就显得尤为重要了。

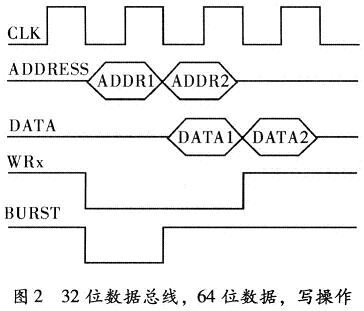

引脚BRST可以用来指示多个传输过程合成一个传输过程,图2是DSP通过32位数据总线写64位数据时序图。

由图2可以看出,数据传输机制与普通流水协议相同,只多了一个BRST指示信号,它与地址1同时有效,表示本次数据没有传输完毕,下次要传输的数据与本次传输的数据是一个整体,即BRST有效时传输是低32位数据,无效时传输的是高32位数据,这样就实现了在32位数据总线上传输64位数据,如果没有BRST信号,该过程会被认为是2次32位传输。

同理,如果用32位数据总线传输128位数据,在传输前3个32位数据的时候,BRST信号有效,传输最后一个32位数据BRST无效。

注意:使用流水协议时,流水深度由传输类型(读数据还是写数据)决定。在写数据传输中,流水深度固定为1;在读数据传输中,流水线深度可由用户编程决定,即由系统配置寄存器SYSCON决定,在1~4之间可变。

2. FPGA设计

由于DSP的协议是相对固定的,FPGA只需按照协议进行设计即可,下面以DSP访问FPGA内部寄存器为例详细介绍。笔者建议采用同步设计,主要信号、输出信号都由时钟沿驱动,可以有效避免毛刺。

为了使所设计的模块通用化,可设流水深度、数据总线位宽、寄存器位宽、寄存器地址可设。笔者建议采用参数化设计,使用参数传递语言GENERIC将参数传递给实体,在实体内部使用外if…else结构,这样在一个程序中可以包含各种情况,但不会增加逻辑的使用量。下面以个别情况为例,详细介绍。

2.1 32位数据总线,32位寄存器,写操作

前面提过,DSP采用流水协议写FPGA时,流水深度固定为1,FPGA在前一时钟沿采到地址、WRx信号有效,在下一时钟沿就锁存数据,如图3所示,FPGA在时钟沿1采到地址总线上的地址与寄存器地址一致,WRx信号为低,写标志信号S_W_FLAG置高,由于采用同步设计,FPGA只有在时钟沿2才能采到S_W_FLAG为高,一旦采到S_W_FLAG为高,FPGA就锁存数据总线上的数据,即在时钟沿2锁存数据。

2.2 32位数据总线,32位寄存器,读操作

与写寄存器不一样,读寄存器时流水深度在1到4之间可设,需要注意的是,为避免总线冲突,DSP不读时,FPGA数据总线应保持三态。

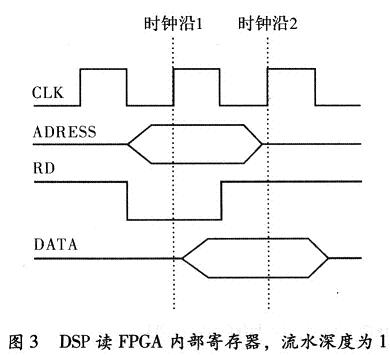

如果流水深度设置为1,FPGA在前一时钟沿采到地址、RD信号有效,应确保在下一时钟沿数据已经稳定的出现在数据总线上,否则DSP不能正确读取数据,如图3所示,在时钟沿1采到地址总线上的地址与寄存器地址一致,RD信号为低,驱动数据总线,在时钟沿2数据已稳定出现在数据总线上,DSP可以读取。

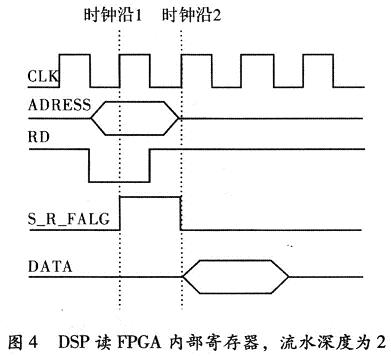

如果流水深度设置为2,FPGA在前一时钟沿采到地址、RD信号有效,应确保隔一时钟周期后,数据稳定的出现在数据总线上,这样就像写操作一样,需要加一个标志,当条件满足,标志为高,一旦标志为高,输出数据,如图4所示。

综上所述,流水深度加深一级,FPGA就晚一个时钟周期驱动数据总线。可以看出,虽然流水深度在1~4之间可设,但是总能保证一个时钟周期传输一个数据。

2.3 32位数据总线,64位寄存器

前面提到,突发流水协议与普通流水协议数据传输机制是一样的,只是多了一个指示信号BRST,当写操作时,FPGA如果在前一时钟沿采到地址、WRx、BRST信号有效,在下一时钟沿就锁存数据到寄存器低位,而如果在前一时钟沿采到地址、WRL有效,而BRST信号无效,在下一时钟沿就锁存数据到寄存器高位。同样,当读操作时,FPGA如果采到地址、RD、BRST信号有效,就将寄存器低位驱动到数据总线上,而如果采到地址、RD有效,BRST而信号无效,就将寄存器高位驱动到数据总线上,具体在哪个时钟沿驱动,由流水深度决定。

3. DSP设置

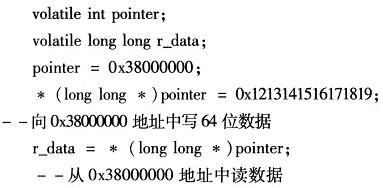

ADSP TS201与FPGA通信时,DSP是否采用流水协议,数据总线位宽,以及流水深度都可以通过系统配置寄存器SYSCON进行设置,SYSCON详细设置见文献[3],以32位数据总线访问64位寄存器为例,一级流水,SYSCON设置为

4. 结束语

文中实现了DSP通过外部总线接口访问FPGA内部寄存器,但是如果需要传输的数据量很大,或者DSP与FPGA的时钟不同步,就不能用寄存器来实现,需要借助于双口RAM或者FIFO,读者可以在本文的基础上加以改进。 |